- Order number: SW10022

SDLC/HDLC and ARCNET Interface module for NI CompactRIO systems offers RS485/422 compatible channels. The module interfaces directly with the CompactRIO FPGA.

The module uses an external power supply to provide maximum compatibility with third party devices.

When combined with the ARCNET corresponding firmware the module can be also used as an ARCNET interface module.

With the module SDLC LabVIEW FPGA Toolkit is provided, which complies with International Standard ISO/IEC 13239.

The Toolkit implements and integrates Synchronous Data Link Control (SDLC) data communication protocol (developed by IBM) in custom applications. SDLC is equivalent to layer 2 of the Open Systems Interconnection (OSI) model of network communication.

The main features of the SDLC toolkit are:

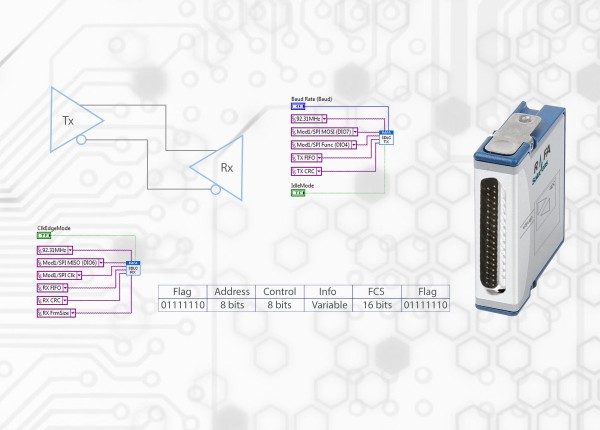

- Separate SDLC Transmitter and Receiver LabVIEW FPGA VIs

- Configurable baud rate

- CRC calculation on the FPGA

- Bit stuffing and unstuffing on the FPGA

- Configurable Clock Edge Mode

The toolkit provides a LabVIEW FPGA Driver Library containing two FPGA VIs, the SDLC TX (transmitter) and the SDLC RX (receiver), for data transmission and reception. Single or multichannel data communication can be implemented with additional drivers, as well as both VIs implement bit stuffing, unstuffing, CRC calculation, and forward error correction to eliminate the need for additional data processing.

SDLC TX FPGA VI transmits data with given Baud Rate which is user-configurable. The VI contains Single Cycle Timed Loop, generates clock according to the given Baud Rate, and includes also Host to Target DMA FIFO for data transmission from Host to Target. SDLC RX FPGA VI receives SDLC data with user-configured clock edge mode (rising/falling edge), contains Single Cycle Timed Loop, and includes also Target to Host DMA FIFO for data transmission and separate Target to Host DMA FIFO for transmission of Frame size.